07 순차 논리 회로

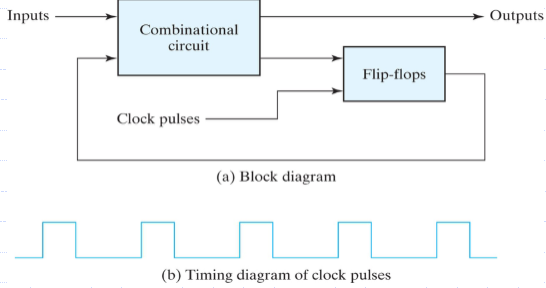

– 출력은 입력과 시퀀서의 현재 상태의 함수입니다.

– 현재 상태는 저장 요소에 의해 제공됩니다.

두 가지 유형의 순차 회로

– Synchronous: 지정된 시간에 입력 신호만을 기준으로 출력이 결정됨

– Asynchronous : 입력 신호에 대한 출력은 임의의 순간에 결정되며 입력 신호가 변경되는 순간 출력이 변경됩니다.

재치

– 동기화 추적 회로에서 동기화가 달성되는 미리 결정된 순간을 나타내는 신호

클럭 순차 회로

– 동기화를 달성하기 위해 메모리 소자의 입력으로 클록 신호를 사용하는 순차 회로

슬리퍼

– 클록 순차 회로에 사용되는 저장 소자

– 1비트의 정보를 저장할 수 있는 이진 저장 요소

– 다중 플립 플롭을 사용하여 다중 비트 저장

– 클록 에지에서만 출력 변경

저장 요소

트리거: 제어 신호의 즉각적인 변화

플립플롭 트리거: 플립플롭의 상태가 변경됩니다.

바

– 플립플롭을 구성하는 기본 회로

– 바이너리 정보를 저장하는데 유용한 회로

– 비동기 순차 회로에 유용한

– 동기식 순차 회로에서는 사용되지 않음(클록 펄스 없음)

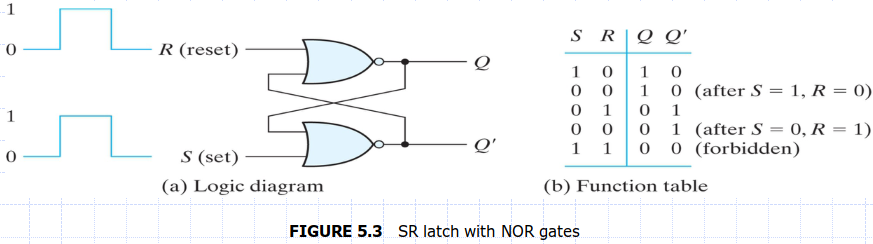

SR 래치

• 2개의 네트워크 NOR 게이트로 구성

S=1, R=0이면 Q=1(단종)

S=0, R=1, Q=0일 때(리셋)

S=0, R=0이면 변화 없음(상태 유지)

S=1,R=1 Q=Q′=0 (Q와 Q’는 다음 입력이 00이 될 때 1과 0을 반복하므로 정의되지 않음)

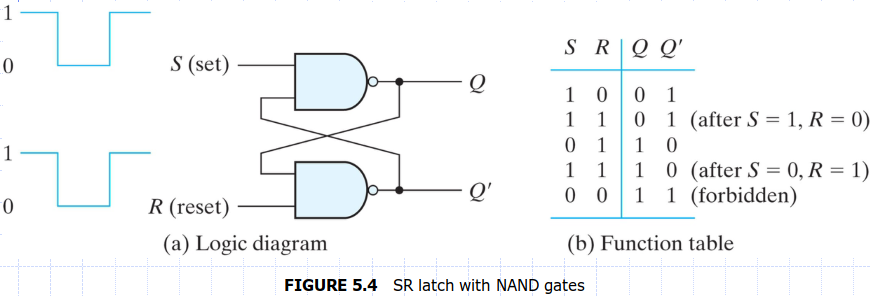

R’S’ 래치

• NOR 래치의 보완을 입력으로 사용

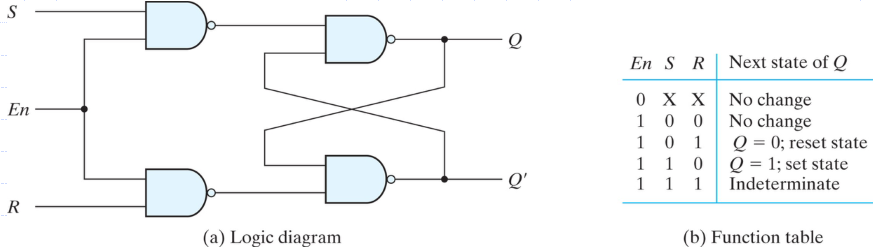

제어 입력이 있는 SR 래치

• 제어 신호를 2개의 NAND 게이트로 결합

En = 0(변경 없음), En = 1(SR 래치로 작동)

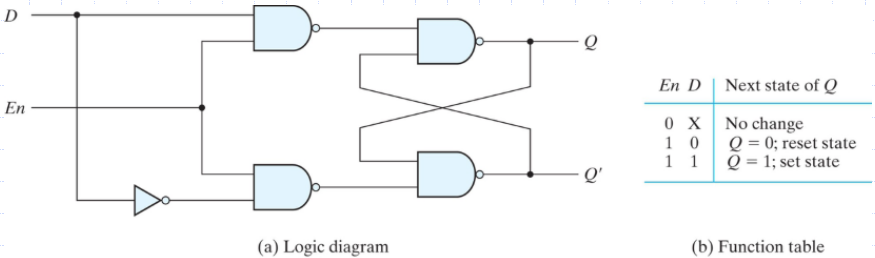

D래치

– SR 래치에서 정의되지 않은 상태 해결

– En = 1이면 출력 값은 D의 값과 같습니다.

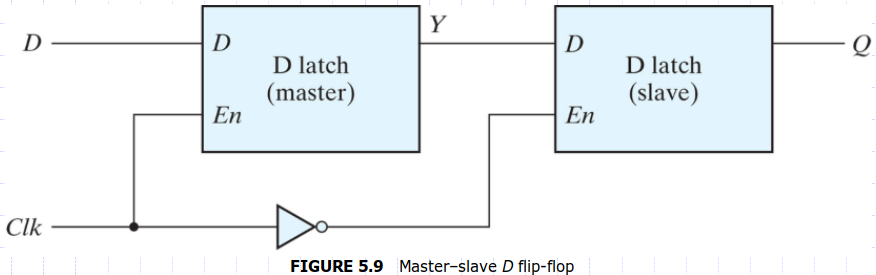

마스터-슬레이브 D 플립플롭

하강 에지 트리거 D 플립플롭

– 하강 에지 트리거 D 플립플롭(위 회로에서 기호 없음 왼쪽의 상승 에지)

Clk=0 : 마스터 정지, 슬레이브 실행. 출력은 입력 상태에 영향을 받지 않습니다.

Clk=1: 마스터 작동, 슬레이브 정지

즉, Q는 하강 에지에서만 입력 D의 동작을 따릅니다.

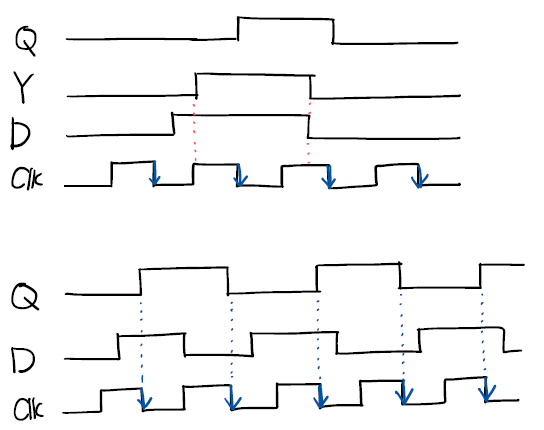

(예제) 위의 마스터-슬레이브 D 플립플롭(falling-edge trigger D flip-flop)의 D와 Clk의 입력 흐름이 다음과 같을 때 출력 Q 흐름을 구하면 다음과 같다.

Q는 클록의 하강 에지에서만 입력 D의 흐름을 따릅니다.

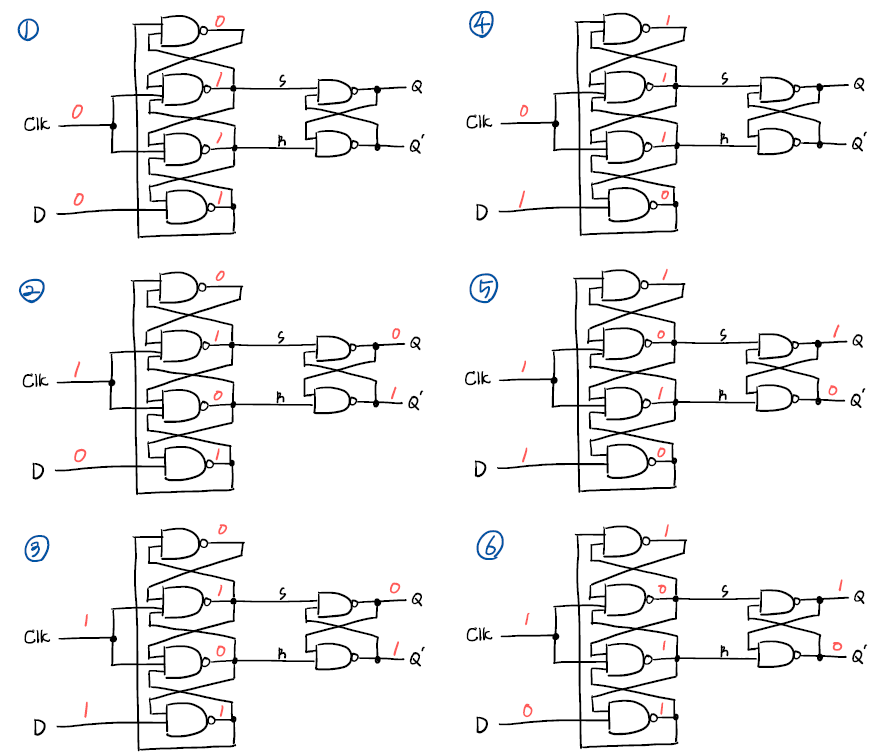

클록 에지 및 입력에 따른 출력의 예

(1) 클럭 0, 입력 0, 출력은 마지막 상승 에지에서 (변경된) 입력 값입니다. 현재 알 수 없음

(2) 클럭 1, 입력 0, 상승 에지부터 출력 상태가 변경됩니다.

(3) 클럭 1, 입력 1, 에지 변화가 없기 때문에 이전 상태를 유지합니다.

(4) 클럭 0, 입력 1, 출력은 마지막 상승 에지에서 (변경된) 입력 값입니다. 현재 알 수 없음

(5) 클럭 1, 입력 1, 출력 상태는 상승 에지이므로 변경됩니다.

(6) 클럭 1, 입력 0, 에지 변화가 없기 때문에 이전 상태를 유지합니다.

클록 순차 회로 분석

– 입력, 출력 및 플립플롭의 상태를 연대순으로 정렬된 표(다이어그램)를 사용하여 분석

– 순차 회로의 등시성 동작은 입력, 출력 및 플립플롭의 현재 상태에 의해 결정됩니다.

– 출력 값과 다음 상태는 입력 값과 현재 상태의 함수입니다.

– 회로도에서 시작하여 상태표(상태도)로 끝난다.

– 회로도 => 입력식 => 상태식(출력식) => 상태표(상태도)

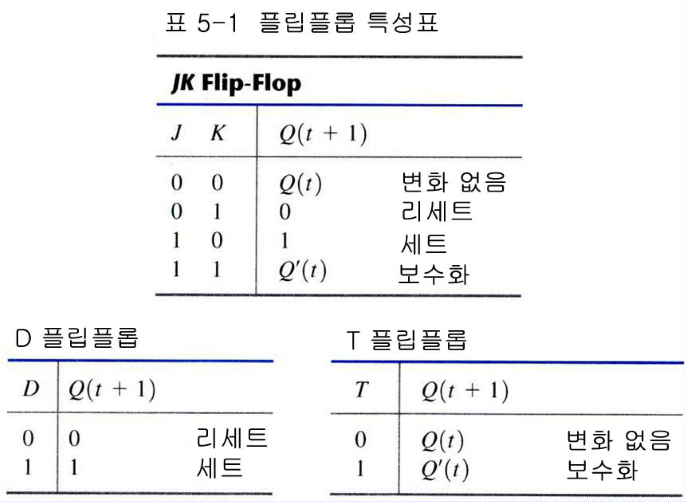

플립플롭 특성표

상태 표현

– 현재 상태와 입력 값이 주어졌을 때 플립플롭의 다음 상태를 지정하는 표현식

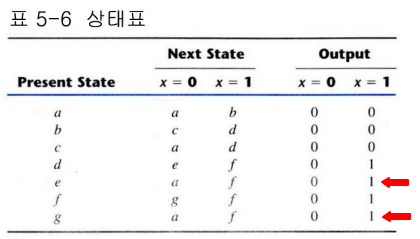

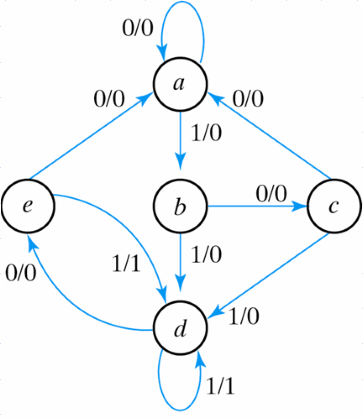

상태 테이블

– 현재 상태와 입력에 대한 다음 상태와 출력을 설명합니다.

– 상태 테이블에는 두 가지 유형이 있습니다.

상태 다이어그램

– 흐름도의 일종

– 상태 테이블에서 가져옴(상태 테이블을 더 읽기 쉽게 함)

– 원(상태), 선(전환), 입/출력으로 구성

디자인 과정

설계 단계

1) 요구되는 규격에서 회로상태도를 얻는다.

2) 필요한 경우 상태 수를 줄입니다.

3) 각 상태에 이진 값을 할당합니다.

4) 바이너리로 인코딩된 상태 테이블을 가져옵니다.

5) 사용할 플립플롭 유형을 선택합니다.

6) 플립플롭의 입출력 방정식을 구하라.

7) 논리도를 그린다.

상태 다이어그램 => 상태 테이블 => 여기 테이블 => 입력 공식(출력 공식) => 회로도

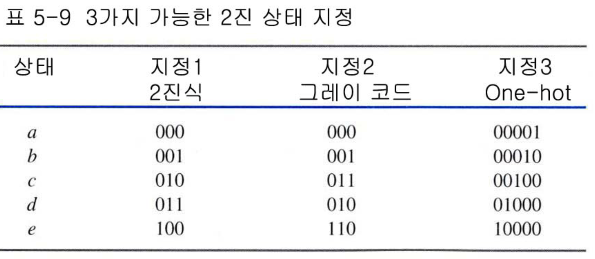

국가 지정 유형

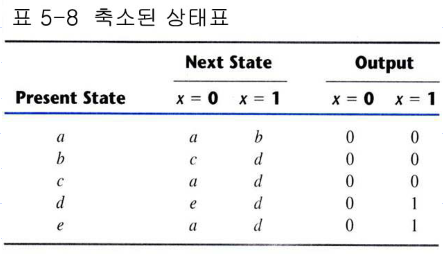

상태 축소 및 할당

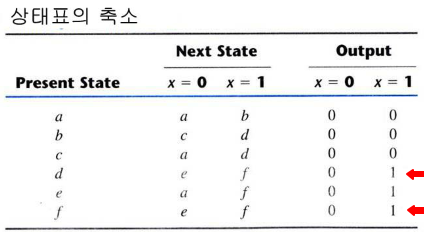

정부 축소

– 순차 회로 설계 과정에서 플립플롭 개수 감소

– 순차회로의 입/출력의 순차변화는 변함없이 유지되어야 한다.

– 두 상태가 동일하면 하나를 제거할 수 있습니다.

-> 두 상태는 모든 입력에 대해 동일한 출력을 제공하고 다음 상태도 동일하면 ‘동등’합니다.

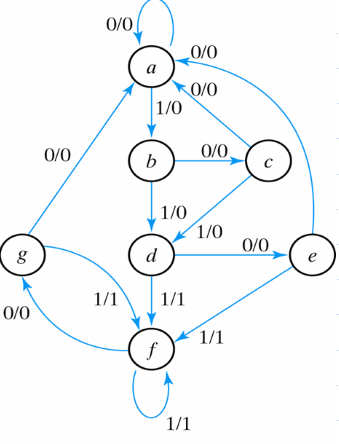

상태 e와 g를 병합할 수 있습니다.

상태 d와 f를 병합할 수 있음

결과

축소 전 상태 다이어그램

축소 상태 다이어그램